# **RESEARCH ARTICLE**

OPEN ACCESS

# Low Power High Speed Folded Cascode Amplifier With PMOS Inputs

B. Krishna M.Tech(VLSI), D. Arun kumar M.E(Embedded systems & VLSI Design) Asst.Prof,Dept of ECE KITE Womens College of Professional Engineering Sciences-SHABAD Asst.Prof,Dept of ECE KITE Womens College of Professional Engineering Sciences-SHABAD

# Abstract

This paper presents the design of low power high speed folded Cascode amplifier with PMOS inputs. The design is carried out using **LTSPICE** tool in **180 nm** CMOS technology.

#### I. Introduction

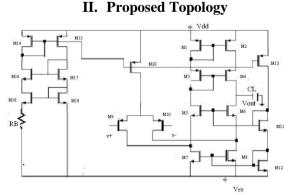

The main aspects of folded Cascode amplifier design are high DC gain, high slew-rate, and high band width. The chosen topology is of PMOS input type and the bias circuit for the proper operation of the circuit is designed. The power supply here is constrained to  $\pm 1.65V$  and the technology used is 180nm.

# Specifications of Folded Cascode Opamp:

| Parameter            | Value       |

|----------------------|-------------|

| Technology           | 180 nm      |

| Power supply         | ± 1.65 V    |

| Gain                 | >50 dB      |

| Slew rate            | 150 V/µsec  |

| Unity gain bandwidth | 150 MHz     |

| Phase margin         | >60 degrees |

| Power consumption    | < 5 mW      |

| PSRR                 | >60 dB      |

| Offset voltage       | -           |

Table 1. Specifications of Folded Cascode op-amp

Fig 1.Folded Cascode with PMOS inputs

#### **III. Design Calculations**

We know that,  $I_{bias} = SR \times C_L = 150 \times 10^6 \times 10^{-12} = 150 \ \mu A$

www.ijera.com

Transconductance, gm =  $2\pi x$  (GBW)x CL = 0.942 m-S

We know that,

gm =  $\sqrt{2Kp\left(\frac{W}{L}\right)}$  Ibias S

Open loop voltage gain of folded cascode Opamp is given by

$A_v = (g_{m9.}g_{m4.}g_{m6})/\{I_D^2(g_{m4.}\lambda_N^2 + g_{m6.}\lambda_P^2)\}$

where,  $g_{m9}$ ,  $g_{m4}$ ,  $g_{m6}$  are the transconductance of the transistors  $M_9$ ,  $M_4$ ,  $M_6$  respectively and  $\lambda_N$  and  $\lambda_P$  are the channel length parameters of NMOS and PMOS respectively. Taking the complementarily between the  $M_6$  and  $M_4$ ,

$g_{m6} = g_{m4}$

Now the gain expression becomes,

$A_v = g_{m9.}g_{m4}/I_D^2(\lambda_N^2 + \lambda_P^2)$

From the above equation calculate, "W" which is found to be  $17\mu m$  which is the size of input transistors. Similarly the second stage in the topology has the bias current of  $150 \ \mu A$  from which we can calculate the remaining aspect ratios of all MOS transistors.

$$\begin{split} &W9 = W10 = 17 \ \mu m \\ &W1 = W2 = W3 = W4 = 14 \ \mu m \\ &W5 = W6 = W7 = W8 = 5 \ \mu m \\ &W11 = W12 = 5 \ \mu m. \end{split}$$

Constructing the bias circuit of an Op-amp to provide the required bias current. Transistor transconductance is the most important parameters in Opamp that must be stabilized. In general biasing of an Opamp is to ensure the proper operation of the circuit.

From the above circuit, writing KVL for the bottom loop in the bias circuit,

$$\begin{split} &V_{gs19} = V_{gs18} + I_{D18}.R_B \\ &\text{And we know, } V_{eff} = V_{gs} \text{-} V_t \\ &V_{eff19} = V_{eff18} + I_{D18}.R_B \hspace{0.2cm} ; \hspace{0.2cm} (W/L)14 = (W/L)15 \\ & \mathcal{K}_{I_{D18}} = I_{D19} \end{split}$$

$$\begin{split} \sqrt{2\frac{\text{ID 19}}{\text{Kn }(\text{W/L})\text{19}}} &= \sqrt{2\frac{\text{ID 18}}{\text{Kn }(\frac{\text{W}}{\text{L}})\text{18}}} &+ \text{I}_{\text{D18}}\text{R}_{\text{B}} \\ \frac{2}{\sqrt{2\text{ ID 19Kn }(\frac{\text{W}}{\text{L}})\text{19}}} \Biggl\{ 1 - \frac{\sqrt{(\frac{\text{W}}{\text{L}})\text{19}}}{\sqrt{(\frac{\text{W}}{\text{L}})\text{18}}} \Biggr\} = \text{R}_{\text{B}} \end{split}$$

We know,

$$gm19 = \sqrt{2Kn \left(\frac{W}{L}\right) 19ID19}$$

$$\frac{2}{\text{gm19}} = \frac{\text{RB}}{\left\{1 - \frac{\sqrt{\left(\frac{W}{L}\right)19}}{\sqrt{\left(\frac{W}{L}\right)18}}\right\}}$$

$$\text{gm19} = \frac{2}{\text{RB}} \cdot \left\{1 - \frac{\sqrt{\left(\frac{W}{L}\right)19}}{\sqrt{\left(\frac{W}{L}\right)18}}\right\}$$

From the above expression it is to be noted that aspect ratios of M18 and M19 should never be the same. For the special case,

$$\left(\frac{W}{L}\right)18 = 4\left(\frac{W}{L}\right)19$$

$$119 = 1/R_{\rm P}$$

Therefore,  $gm19 = 1/R_B$

So, simply the trans-conductance depends on the resistance  $R_B$  Adjust this  $R_B$  to obtain your required biasing current.

Aspect ratios of the MOS transistors are as follows: W14 = W15 = W16 = W17 &

$$14 = W15 = W16 = W17$$

$W18 = 4W19$

### IV. Simulation results of Folded Cascode Opamp

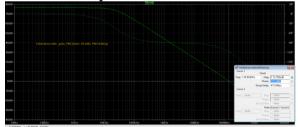

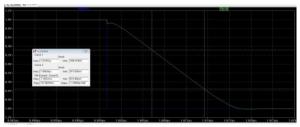

Gain and Phase plot

Fig 2 Gain and Phase plots of Folded Cascode Opamp with biasing circuit

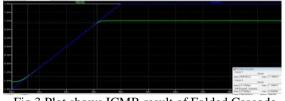

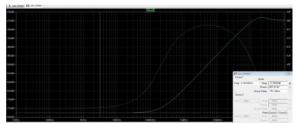

#### Input Common Mode Range (ICMR):

For the calculation of ICMR, connect the Opamp in feedback and apply a ramp input to the non-inverting terminal and perform the transient analysis, the output is plotted as shown in below fig

Fig 3 Plot shows ICMR result of Folded Cascode Opamp

From the above graph, the common mode input range is found to be -1.39V to 1.10V.

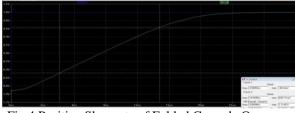

#### Slew rate (SR):

Slew rate of an Op amp is defined as the maximum rate of change of output for the small change in input

$$SR = \left[\frac{dVo}{dt}\right]_{max}$$

Generally SR is determined from the slope of output waveform during rise or fall of the output when the input is applied. So, we have a positive SR and a negative SR

Fig 4 Positive Slew rate of Folded Cascode Opamp

Fig 5.Negative Slew rate of Folded Cascode Opamp

From the above graph it is inferred that positive  $SR = 117 V/\mu sec$

And negative SR = -120 V/ $\mu$ sec

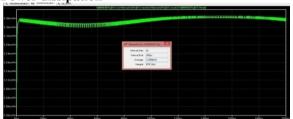

### V. PSRR of a Folded Cascode Opamp:

PSRR performance of an Opamp can be found by applying a small sinusoidal signal to the power supply

The following fig. shows the graph of PSRR. In general, this value should be as high as possible over a wide range of frequency.

Fig 6 PSRR of Folded Cascode Opamp

### Positive PSRR=77dB Negative PSRR=104 dB **Power dissipation**

Fig 7Power dissipation of folded cascode op-amp

| Parameter         | Value            |

|-------------------|------------------|

| Gain              | 77 dB            |

| Phase Margin      | 63 degrees       |

| Unity gain        | 140 MHz          |

| frequency(UGF)    |                  |

| Offset voltage    | 31 µv            |

| SR+               | 117 V/µs         |

| SR-               | -120 V/µs        |

| PSRR+             | 77 dB            |

| PSRR-             | 104 dB           |

| ICMR              | -1.39 V to 1.10V |

| Power dissipation | 3.39 mW          |

VI. Summary of folded cascode op-amp

Table 2 Summary of folded Cascode op-amp

### VII. Conclusions

In this thesis, a Low power high speed folded Cascode op-amp capable of providing high gain(77dB) and High speed with more stable(Phase margin=63) is designed in **LTSPICE with 180nm CMOS technology**. Simulation results are observed that circuit dissipates very low power.

### Refernces

- [1] P. Phillip E Allen and Douglas R. Holdberg "CMOS analog circuit design" Oxford series.

- [2] Houda Daoud, Samir Ben Salem, Sonia Zouari,Mourad Loulou, "Folded Cascode OTA Design for Wide Band Applications", Design and Test of Integrated Systems in Nanoscale Technology, 2006.

- [3] Raghuwar Sharan Gautam, P. K. Jain, and D. S. Ajnar3 "Design of Low Voltage

Folded Cascode Operational Transconductance. Amplifier with Optimum Range of Gain and GBW in 0.18µm Technology". Raghuwar Sharan Gautam,P. K. Jain,D. S. Ajnar/ International Journal of Engineering Research and Applications (IJERA) Vol. 2, Issue 1,Jan-Feb 2012.

- [4] M. Banu, J. M. Khoury, and Y. Tsividis, "Fully Differential Operational Amplifier with Accurate Output Balancing," IEEE Journal of Solid State circuits, Vol. 23, No. 6, pp. December 1990.

- [5] Arash Ahmadpour, Pooya orkzadeh" An Enhanced Bulk-Driven Folded-Cascode Amplifier in 0.18 μm CMOS Technology" Circuits and Systems, 2012, 3, 187-19 doi:10.4236/cs.2012.32025 Published Online

- [6] Swati Kundra1, Priyanka Soni2 and Anshul Kundra "Low Power Folded Cascode OTA "International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.1, February 2012

VIII. About Authors

# Mr.B.Krishna

completed **B.Tech** in ECE From Dr.Paul-Raj Engineering College Bhadrachalam(JNTUH) in 2005 and ,**M.Tech**(VLSI-SD) From SITAMS-Chittoor(JNTUH) in 2008. Presently he is working in **KITE Womens College of Professional Engineering Sciences as a Asst. Professor**

# Mr. D.Arunkumar-

**Graduated(B.Tech)** from Vaagdevi College Of Engineering in Electronics and Communication Engineering and **Master in Engineering** from Vasavi college of Engineering in Embedded Systems and VLSI Design. Presently he is working in **KITE Womens College of Professional Engineering Sciences as a Asst. Professor**